-- Veröffentlicht durch Stuzzy am 18:37 am 9. Okt. 2005

so isses, darum lohnt es sich auch kaum^^

-- Veröffentlicht durch Cr4cky am 13:51 am 9. Okt. 2005

Zitat von Stuzzy um 18:49 am Okt. 8, 2005 @Cr4cky: schauen, was man tun muss, um den Cahce freizuschalten, der vllt. von AMD dektiviert wurde... und wenn mans über die pins machen will gibbet da 754hoch754 varianten:D (=754^754) |

ach du sch****e... (sry) also alle möglichen pins miteinander verbinden?!

heilige... dannach hat man entweder ne schrotte cpu, aufgeschnittene finger oder beides xD

-- Veröffentlicht durch MagicPocket am 22:29 am 8. Okt. 2005

und so gering wie der preisunterschied zwischen nem 128er und nem 256er Sempron 64 ist lohnts eh kaum. |

Es geht ja nicht nur um die 128kb Sempis sondern auch um die 256kb Sempis die man dann mit dem gleichen Verfahren auf 512kb ( bloss wie) freischalten könnte.

-- Veröffentlicht durch Stuzzy am 18:49 am 8. Okt. 2005

@Cr4cky: schauen, was man tun muss, um den Cahce freizuschalten, der vllt. von AMD dektiviert wurde... und wenn mans über die pins machen will gibbet da 754hoch754 varianten:D (=754^754)

-- Veröffentlicht durch Cr4cky am 18:30 am 8. Okt. 2005

frage: was gibts denn ausprobieren???

weil ich blicke da nicht so ganz durcj, wovon ihr redet...

was genau ausprobieren, um "mehr" cache freizuschalten...

danke...

(möchte ja schließlich ein wenig dazu lernen, wenn ich hier immer mitlese)

mfg Cr4cky

-- Veröffentlicht durch Henro am 18:21 am 8. Okt. 2005

naja wie dem auch sei braucht man erstmal korrekte vergleiche ... also n 754er Sempron64 mit 128kb sowie 256kb und am besten noch n 512kb venice.

Und wenn man die hat müsste sich immer noch jemand finden der bock hat geld aufs spiel zu setzen um da eventuell was zu probieren.

fazit = ziemlich aussiechtslos ;)

und so gering wie der preisunterschied zwischen nem 128er und nem 256er Sempron 64 ist lohnts eh kaum.

-- Veröffentlicht durch MagicPocket am 12:00 am 8. Okt. 2005

Zitat von Henro um 9:47 am Okt. 7, 2005 wenn man sich die fotos mal anschaut dann sieht man aber auch das auf dem palermo nicht alle lötpunkte überhaupt vorhanden sind ! wäre noch interessant zu wissen obs n 128er oder n 256er palermo ist ! |

Hab den Artikel gerad mal durchgelesen zu den PIC`s.

Es ist ein 256kb Cache Palermo.

-- Veröffentlicht durch Fiasco am 15:06 am 7. Okt. 2005

Zu den von mir beim Marktplatz von Hardwareluxx gemopsten Bildern:

Bei dem Venice handelt es sich um einen mit E3-Stepping.

Der Sempron ist ein Sempron64 mit E6-Stepping. Wenn jetzt noch jemand ein Bild von einem geköpften E6-Venice hat, wäre geklärt, ob die neueren weniger Lötpunkte haben (wovon ich ausgehe...).

Vor mir habe ich noch einen AthlonXP 2800+ für S754 liegen (quasi ein PräSempron mit Clawhammerkern - sagt jedenfalls CPU-Z). Der besitzt leider ebenfalls nur 128KB Cache, hat aber einen relativ großen quadratischen Kern (viell. Platz für 512KB ?). Merkwürdigerweise fehlen aber im Gegensatz zum Sempron64 keinerlei Bausteine :noidea: Viel Platz für weitere Lötpunkte ist auch nicht...

-- Veröffentlicht durch Stuzzy am 14:01 am 7. Okt. 2005

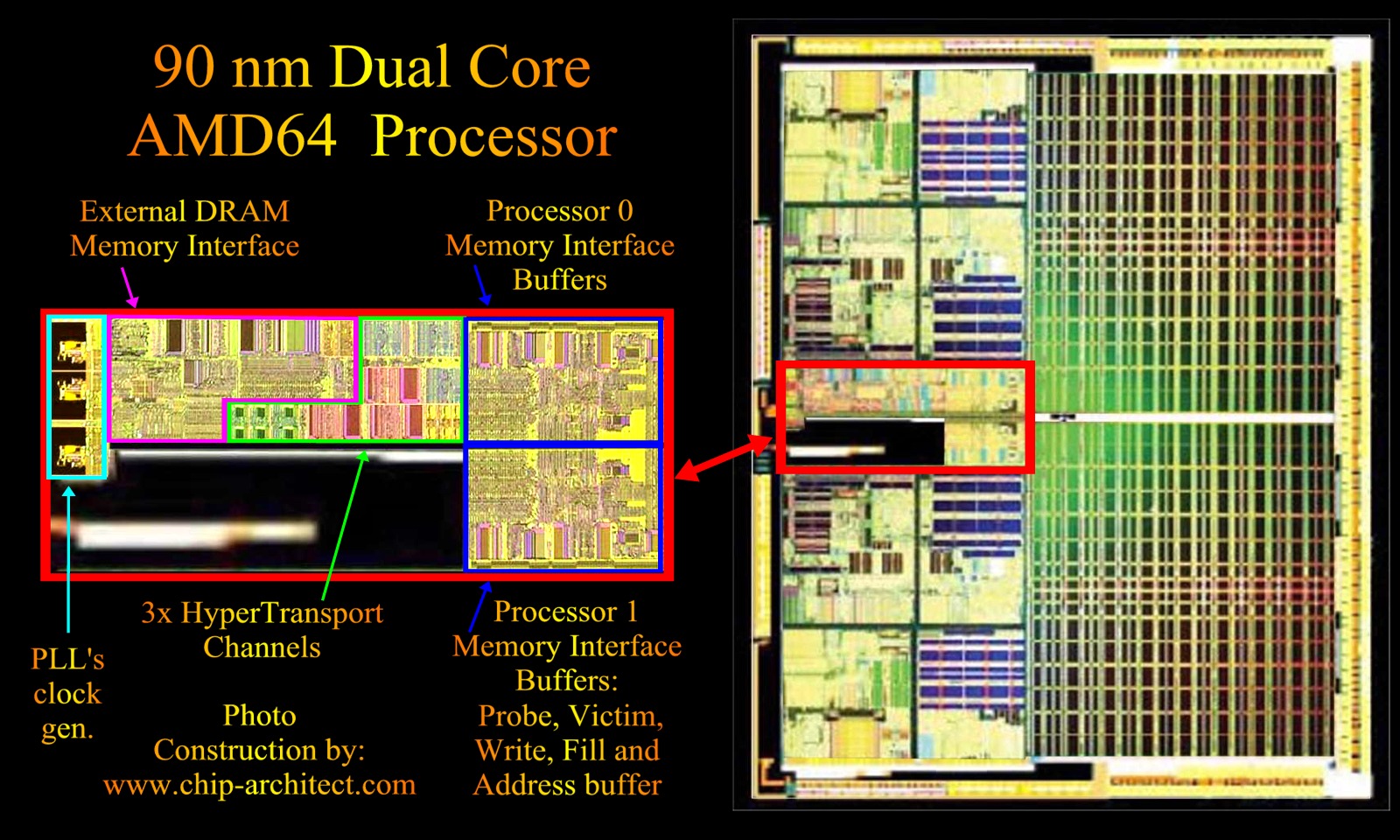

ein ähnliches bild wie das hier wäre von beiden CPU's sinnvoll:

-- Veröffentlicht durch Henro am 13:19 am 7. Okt. 2005

ne das meiste werden wie beim P4 kondensatoren sein um zu puffern ... aber mit mutmassungen und geschichten ausm nähkästchen kommen wa nicht weiter.

Mehr bilder zum vergleichen wären nicht verkehrt.

-- Veröffentlicht durch MagicPocket am 12:53 am 7. Okt. 2005

Also der Cache ist ja komplett im "Die" integriert!

Deshalb kann ich mir nicht vorstellen das die Lötpunkte was mit Cache zu tun haben sollen.

Ich vermute stark, das der "Palermo" deshalb weniger Lötpunkte hat, da er im Fertigungsverfahren optimiert wurde, und deshalb weniger Lötpunkte nötig waren

-- Veröffentlicht durch Henro am 10:22 am 7. Okt. 2005

tja irgendjemand müsste sich halt opfern :)

mein gedanke war nur das der palermo ja durchaus ein kern mit max. 256kb cache sein kann ... also das nur 256kb vorhanden sind und das dann davon die hälfte abgeschaltet wird teilweise.

-- Veröffentlicht durch kammerjaeger am 10:19 am 7. Okt. 2005

Die Frage ist eben nur, ob die fehlenden Lötpunkte was mit dem Cache zu tun haben oder eher z.B. für die Pinbelegung und den Speichercontroller wichtig sind, was für die Cachefreischaltung zweitrangig wäre...

-- Veröffentlicht durch Henro am 9:47 am 7. Okt. 2005

wenn man sich die fotos mal anschaut dann sieht man aber auch das auf dem palermo nicht alle lötpunkte überhaupt vorhanden sind !

wäre noch interessant zu wissen obs n 128er oder n 256er palermo ist !

-- Veröffentlicht durch Stuzzy am 0:44 am 7. Okt. 2005

probiert doch mal:) gibt ja nur 754^754 lösungen:D (meines wissens:noidea:)

btw: mit was kann man sowas hoher ausrechnen?

-- Veröffentlicht durch kammerjaeger am 23:05 am 6. Okt. 2005

Zitat von smoke81 um 19:23 am Okt. 6, 2005 @ kammerjaeger Hast Du grad mal Super PI 1 M- Werte von Deinen beiden PCs im Kopf? |

Nö. SuperPI ist mir zur theoretisch, daher benche ich es nicht... ;)

-- Veröffentlicht durch MagicPocket am 22:45 am 6. Okt. 2005

Fettes Lob für die Photos von dir :thumb:

Das lässt doch darauf schließen, dass beide Cores theroretisch die gleiche Cachegröße "Onboard" haben müssen.

Nur ist da echt nix von Brücken zu sehen beim Palermo.

Hilft hier vielleicht die gute alte "Drahtmethode" an den Pins weiter : noidea:

-- Veröffentlicht durch Fiasco am 22:32 am 6. Okt. 2005

Ich habe jetzt mal 2 Pics von CPUs ohne Heatspreader gefunden.

Da wäre zum einen Venice:

Und hier ein Palermo:

Für mich sehen die Kerne gleich groß aus :)

Merkwürdigerweise fehlen aber beim Palermo ein paar "Bausteine" :noidea:

-- Veröffentlicht durch Fiasco am 22:09 am 6. Okt. 2005

Wie gesagt: Bedingung ist, dass die Kerne von Venice und Palermo gleich groß sind. Vielleicht finde ich ja ein paar Pics von geköpften CPUs...

(Geändert von Fiasco um 22:33 am Okt. 6, 2005)

-- Veröffentlicht durch MagicPocket am 21:36 am 6. Okt. 2005

ich habe mir das so gedacht:

Ich habe selber einen Palermo (Venice E6 Stepping-Kern) KW2305 2600+ 1600MHZ 128kb 2nd Level Cache.

So der "Echte" Venice hat ja 512kb 2nd Level.

Meine logische Schlussfolgerung: Freischalten was das Zeug hält nur wie:blubb:

Das wär zu geil wenn ich auf 512kb freischalten könnte :godlike:

-- Veröffentlicht durch Compjen am 21:27 am 6. Okt. 2005

EVTL ist etwas unter dem kern wo man dran drehn könnte, den Kern ab kriegen isst j aleicht, nur ob man dan wieder nen post vom Prozzie kriegt :lol:

Ich denke wenn ich jetzt mit nem Sempie zu AMD gehe und dei wollen den wirklich unbedingt frei schalten können die das auch, aber wär es für "Sterbliche" möglich dan hätt das schon längst Jemand geknackt ;)

-- Veröffentlicht durch Fiasco am 20:19 am 6. Okt. 2005

Die Palermos haben eindeutig einen Winchester/Venice-Kern. Die Steppings sind absolut identisch. Im Gegensatz zum Applebred wurde noch nicht einmal der erste Buchstabe geändert (JIUHB->MIUHB etc.). Wenn die Kerne von Sempron und A64 auch noch gleich groß sind, läßt das nur den Schluß zu, dass einfach 256KB bzw. 384KB des Caches deaktiviert wurden :noidea:

Dummerweise gibt es aber auf den CPUs keine Brücken mehr. Somit wäre die einzige Lösung wohl: Pinmod...

-- Veröffentlicht durch smoke81 am 19:23 am 6. Okt. 2005

Zitat von kammerjaeger um 19:05 am Okt. 6, 2005 Ist im Grunde doch ein Venice (zumindest die aktuelleren Steppings), nur eben für S.754. Deshalb finde ich die Frage gar nicht so abwegig, besonders beim Sempron64. ;) |

Dann könnte man die alten 130nm CPUs für S754 endgültig einschmelzen :lol:

@ kammerjaeger

Hast Du grad mal Super PI 1 M- Werte von Deinen beiden PCs im Kopf?

-- Veröffentlicht durch kammerjaeger am 19:05 am 6. Okt. 2005

Ist im Grunde doch ein Venice (zumindest die aktuelleren Steppings), nur eben für S.754.

Deshalb finde ich die Frage gar nicht so abwegig, besonders beim Sempron64. ;)

-- Veröffentlicht durch Gibtnix am 19:02 am 6. Okt. 2005

Zitat von Fiasco um 18:09 am Okt. 6, 2005

Woher weißt du das so genau? :noidea: |

der Sempron ist afaik ein völlig eigenständiger Kern, der nichts mit einem Newcastle oder Clawhammer zu tun hat. Von daher sind da auch nur 256 KB L2 (oder wie viel L2 hat der?:noidea:) "eingebaut".

Beim Duron Applebred z.B. war es so, dass das einfach ein T-Bred war, der einen Teil L2 Cache deaktiviert hatte. Beim Sempron ist das aber nicht so.

-- Veröffentlicht durch Fiasco am 18:09 am 6. Okt. 2005

Zitat von Coolzero2k1 um 17:06 am Okt. 6, 2005 nein geht nicht! |

Woher weißt du das so genau? :noidea:

-- Veröffentlicht durch Coolzero2k1 am 17:06 am 6. Okt. 2005

nein geht nicht!

-- Veröffentlicht durch MagicPocket am 16:52 am 6. Okt. 2005

Hallo,

kam eigendlich schon mal einer auf die Idee den Heatspreader abzumachen, und rauszukriegen ob man den 2n Level Cahe des Semprons irgendwie freischalten kann?

Muß doch bestimmt irgendwie klappen :blubb: